以下文章来源于逍遥设计自动化;作者逍遥科技

引言

人工智能、云计算和高性能计算的快速发展对现代数据中心的数据传输带宽和能源效率提出了更高的要求。传统的可插拔光学模块虽然在维护和升级方面具有便利性,但随着网络交换机容量超过12.8太比特每秒,这些模块已经成为性能瓶颈。交换机ASIC与前面板光收发器之间的长电气走线会引入显著的插入损耗、串扰,功耗可达15到20皮焦耳每比特。光电共封装技术和3D光电子集成技术为这些挑战提供了新的解决方案,从根本上重新定义了光学组件和电子组件在单一封装内的协同工作方式[1]。

01从可插拔模块到光电共封装技术的演进

光电共封装技术的发展历程体现了对更高带宽密度和更低功耗的持续追求。在2000年代初期,光收发器主要作为可插拔模块存在于服务器板的外围位置,遵循SFP和QSFP等标准,这些标准使得灵活部署和系统升级变得容易。然而,随着总交换容量不断攀升,ASIC与可插拔光模块之间的电气互连因为印刷电路板长走线上的插入损耗、串扰和高功耗而变得越来越成问题。

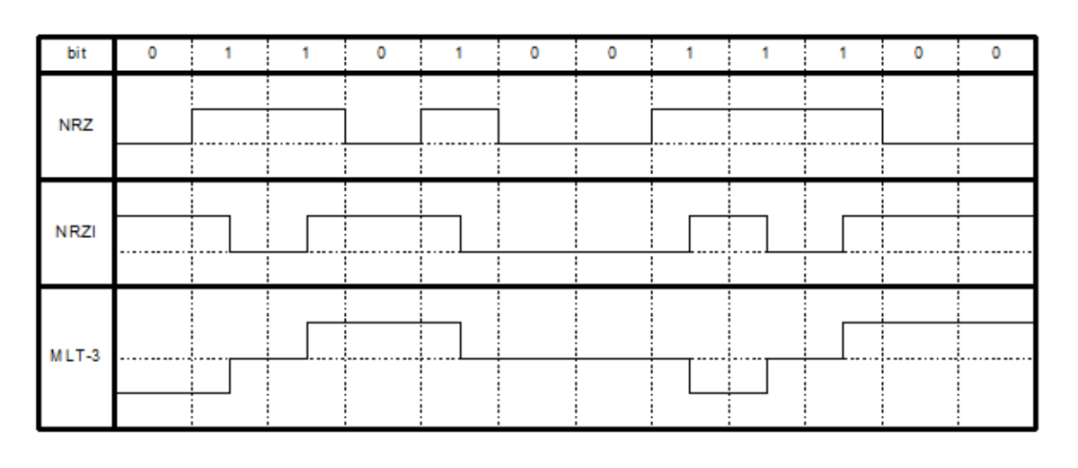

图1:从可插拔收发器到光电共封装技术的演进过程,显示了光学和电气组件如何随时间逐步靠近ASIC,在每个阶段都减少了互连长度并降低了功耗。

业界首先尝试通过板上光学模块来解决这些限制,将光引擎放置在与交换ASIC相同的电路板上,位置更靠近ASIC。这种方法缩短了电气路径长度,部分缓解了信号劣化问题,同时相比传统可插拔模块降低了能耗。尽管有这些改进,板上光学模块设计仍然受到机械和热约束的限制,这限制了其在需要多太比特总带宽的下一代系统中的可扩展性。

光电共封装技术将集成推向了新的高度,通过使用硅interposer、硅通孔和异质集成方法,将光收发器直接安装在与交换ASIC相同的封装内。通过在共同基板上将光学和电子器件紧密放置,光电共封装技术将电气链路长度大幅缩短至仅几毫米,将能耗降低到5至10皮焦耳每比特的范围,同时增强信号完整性,实现25.6太比特每秒及更高的总带宽。

02理解2.5D和3D集成策略

从传统2D封装到先进的2.5D和3D集成的转变代表了光电子集成芯片和电子集成线路在物理排列和电气连接方式上的基础性转变。在传统2D封装中,光电子集成芯片和电子集成线路并排放置在共享基板上,通过引线键合或倒装芯片技术连接。虽然这种方法在制造角度相对简单,但较长的横向互连限制了性能并增加了寄生损耗。

图2:从2D到3D集成的电子和光电子集成芯片集成选项演进,显示了每种方法如何通过日益复杂的封装架构减少互连长度并提高带宽密度。

2.5D封装在芯片和封装基板之间引入了interposer层。这种interposer通常由硅或玻璃制成,包含硅通孔或玻璃通孔,在芯片之间实现高密度垂直连接和精细间距横向布线。硅interposer提供出色的布线密度和精细间距连接,使其在高性能计算和GPU集成应用中得到广泛部署。然而,硅interposer成本较高,并且由于体硅层的存在可能带来散热挑战。带有玻璃通孔的玻璃interposer已经成为有吸引力的替代方案,提供更低的射频衰减、更好的机械性能,以及潜在的更低制造成本。

英特尔的嵌入式多芯片互连桥(EMIB)代表了另一种2.5D变体,将小型硅桥嵌入有机基板中,创建局部高带宽互连,而无需在整个封装上使用完整的interposer。这种方法在需要的地方提供出色的电气性能,同时通过限制昂贵硅面积的使用来保持成本效益。在所有2.5D配置中,芯片保持在interposer表面上横向放置,与标准2D方法相比最小化了互连长度,同时保持相对简单的热管理,因为芯片不会直接堆叠在彼此之上。

真正的3D集成采用根本不同的方法,通过垂直堆叠芯片,通过垂直互连创建直接的芯片到芯片连接。在这些系统中,光电子集成芯片可以作为具有类似硅通孔的垂直连接的interposer层,或者光电子芯片和驱动线路可以使用混合键合等先进技术直接正面对背面键合。这种架构实现了最短的互连长度和最低的插入损耗,直接转化为能源效率和带宽密度的改善。最近的3D堆叠CPO引擎演示已经实现了每秒多太比特的吞吐量,证明了垂直集成架构的技术可行性。

然而,3D集成引入了必须仔细管理的严重热和机械挑战。当高功率ASIC直接堆叠在热敏感的光电子集成芯片上方时,来自ASIC的热量会导致光学谐振器的波长漂移、激光器效率下降以及调制器性能不稳定。先进的热管理策略变得必不可少,包括使用高导热性的热界面材料、金属散热片、热电冷却器,在某些情况下,还包括集成在interposer或基板内的微流体冷却。

03硅基光电子与VCSEL方法的比较

CPO的实现沿着两条不同的技术路线发展,每条路线在性能、成本和应用要求之间提供不同的权衡。基于硅基光电子的CPO利用成熟的互补金属氧化物半导体制造基础设施在硅基板上创建集成光子线路。这些系统通常在1310纳米或1550纳米附近的电信波长工作,与单模光纤接口,实现高达2公里的扩展传输距离。硅基光电子在需要密集波分复用的应用中表现出色,在密集波分复用中,不同波长的多个光通道共享同一根光纤,显著增加总带宽密度。

硅基光电子与现有CMOS代工厂的兼容性为在超大规模数据中心和电信互连中扩展到多太比特吞吐量提供了清晰的路径。先进的硅光电子收发器在商业原型中已经证明了接近5到10皮焦耳每比特的能源效率,实验室演示在优化条件下将这一范围进一步降低。然而,硅基光电子在封装成本和assembly公差方面面临挑战,特别是在与单模光纤的精确对准方面,即使是微米级的对准偏差也会导致显著的耦合损耗。

基于垂直腔面发射激光器的CPO采用不同的方法,在850到1060纳米之间的较短波长工作,通常与多模光纤接口。VCSEL阵列展示了卓越的能源效率,一些实现在短距离链路上达到1到2皮焦耳每比特。多模光纤的较大纤芯直径大大放宽了与单模光纤耦合相比的对准公差,简化了封装并降低了制造成本。IBM和Coherent的MOTION项目等工业原型验证了紧凑的玻璃基板VCSEL模块,具有皮焦耳每比特级的能源效率和高集成密度。

图3:用于51.2太比特每秒交换机的CPO模块详细结构,说明了ASIC、电子集成线路和光电子集成芯片在共同基板上的异质集成以及全面的热管理系统。

基于VCSEL方法的主要限制是传输距离,在多模光纤上很少超过几百米。单模VCSEL的最新发展旨在扩展可能的链路距离,可能会模糊短距离VCSEL和长距离硅基光电子之间的传统界限。硅基光电子和基于VCSEL引擎之间的最终选择在很大程度上取决于系统级因素,包括每通道所需的数据速率、现有光纤基础设施、成本目标、热预算,以及应用是优先考虑扩展传输距离还是在较短距离上最大化能源效率。

04制造和生产挑战

要在商业规模上充分发挥CPO和3D光电子技术的潜力,需要克服几个制造和生产方面的挑战。硅基光电子和混合集成中的良率和工艺控制仍然是活跃的研究领域,特别是随着III-V增益材料在硅上的芯片键合和晶圆级异质集成技术的成熟。光刻、沉积和键合步骤中的工艺变化会导致光学谐振器的波长偏移和耦合效率低下,从而导致大量良率损失。正在开发先进的工艺监控技术、统计建模方法和面向良率的设计方法,以最小化性能分散并实现可接受的生产良率。

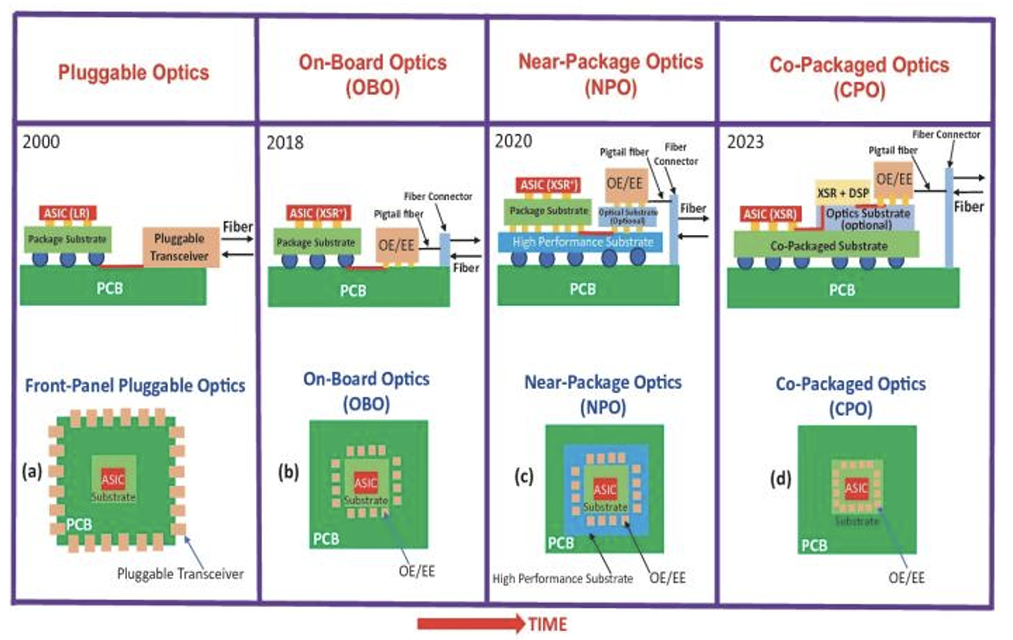

图4:使用玻璃interposer技术和微凸点键合在共封装基板上ASIC、电子集成线路和光电子集成芯片的3D异质集成的制造工艺。

对准公差和耦合损耗在先进封装中构成显著障碍,其中光纤或波导之间轻微对准偏差导致的插入损耗会严重降低整体链路预算,特别是在更高数据速率下。为了应对这些挑战,研究人员开发了无源对准结构、自对准耦合接口和3D打印波导,作为放宽assembly公差同时保持低损耗的方法。光纤连接和芯片到芯片互连的新方法,如光栅耦合器和带有点尺寸转换器的边缘耦合,正在密集开发中,以降低成本并简化制造复杂性。

图5:来自APSUNY的硅基光电子PDK,显示了基于玻璃的interposer集成的示意工艺,包括微凸点键合和铜到铜混合键合配置。

热可靠性和功耗管理对于避免密集光电封装中的性能漂移和过早失效非常关键。温度波动会影响硅和其他材料的折射率,导致谐振偏移并随时间增加插入损耗。新型封装解决方案采用高导热基板、先进散热方法,以及热敏感性降低的设计,如无热波导和微谐振器。通过改进的器件设计(包括硅上量子点激光器和低电压调制器)降低整体发热量,有助于在高数据吞吐量条件下保持稳定运行。

大规模制造的可扩展性必须得到解决,以满足数据中心和新兴高速光链路的需求。从小众研究规模制造过渡到标准化300毫米CMOS生产线涉及适配代工厂兼容设计、确保大晶圆上的工艺均匀性,以及实施多项目晶圆流片,使多个客户能够分担制造成本。晶圆级键合、微转印和基于chiplet的集成等技术正在获得动力,用于实现大规模异质光电系统,具有更高的吞吐量和更低的每个芯片成本。

光子技术生态系统历史上缺乏电子行业数十年来享有的组件库、设计规则检查和自动化布局的统一基础设施。具有全面组件库、紧凑模型和经过验证的工艺配方的标准化工艺设计套件将加速CPO和3D光电子技术的产品开发周期并缩短上市时间。虽然考虑到不同代工厂的专有器件库和设计规则,完全的跨代工厂统一性仍然不现实,但该行业正在朝着标准化建模方法和设计验证流程迈进,以实现可移植性。在封装和assembly层面,标准化的理由更加充分,新兴的封装和assembly设计套件定义了关键的接口规范,包括光学和电气输入输出引脚排列、光纤连接几何形状、对准公差以及直接影响互操作性的热和机械约束。

05从数据中心到量子网络的应用

CPO和3D光电子集成的融合继续通过增加的带宽能力、降低的功耗和增强的可扩展性来改变多个行业。在超大规模数据中心和人工智能集群中,对能够实时传输大量数据的高密度、低功耗互连的需求推动了集成光学技术的快速采用。通过将光收发器直接与网络交换ASIC集成,CPO降低了传输损耗和功耗,同时降低了总拥有成本。新兴方法利用3D光电子封装将垂直腔面发射激光器和光电子chiplet集成到同一封装中,随着人工智能工作负载持续增加,实现了高比特率和改进的系统可靠性。

在高性能计算系统中,随着计算能力向百亿亿次级扩展,带宽瓶颈和热约束构成了显著挑战。集成光子互连为传统铜链路提供了有吸引力的替代方案,在大幅降低功耗预算的情况下提高了性能。3D光子集成已经成为开发可行的量子网络和混合量子计算节点的核心,为光子产生、路由和检测提供紧凑和稳定的架构。在封装级别结合电子和光电子组件可实现下一代高性能计算和新兴量子应用所需的超低延迟通信基础设施。

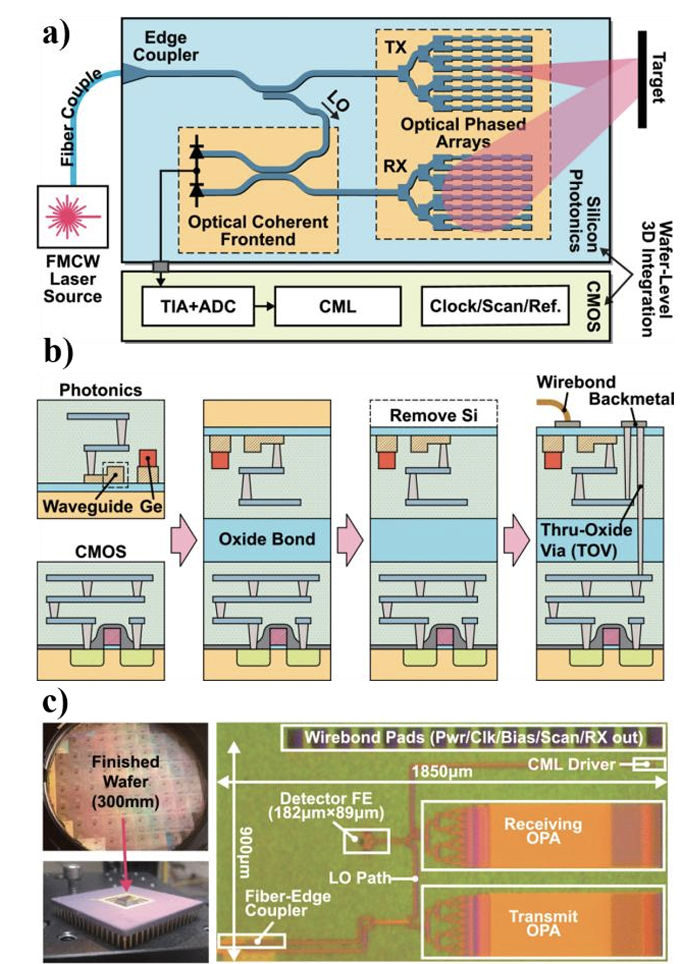

图6:集成相干激光雷达系统的系统架构和芯片照片,展示了如何在紧凑的光电封装中通过全双工光链路连接处理器和存储器。

未来的第五代和第六代移动网络依赖于密集的前传和回传链路,这些链路需要高数据速率、灵活的部署能力和出色的信号完整性。CPO可以通过将光学接口与基带处理ASIC共同定位来显著降低集中式无线接入网络中的功耗。3D光电子封装促进了射频和光电子组件的无缝集成,支持下一代模拟和数字前传解决方案,这些解决方案提高了频谱效率和网络可扩展性,用于大规模连接器件和超低延迟通信。

图7:用于相干激光雷达的硅基光电子与CMOS的晶圆级3D集成,包括制造细节以及带有封装器件的完整300毫米晶圆。

用于自动驾驶车辆的光学传感和激光雷达系统将从集成光子技术的进步中大量受益,特别是随着汽车行业向高分辨率固态解决方案发展。在单个3D光电子封装中集成光学相控阵、相干检测线路和信号处理模块可以减小外形尺寸,同时提高性能。片上光子激光雷达架构旨在实现更紧凑和更节能的传感器,这对于在苛刻的真实世界环境中实现稳健和安全的自主导航非常关键。

航空航天和国防部门需要用于卫星通信和雷达系统的安全、高带宽且通常具有抗辐射能力的光链路。3D集成光电子技术可以通过在紧凑封装中将光收发器与电子控制线路合并,减轻基于空间平台的尺寸、重量和功率挑战。微波光子技术和光波束成形技术同样通过紧凑的共封装模块得到增强,在可靠性和性能至关重要的雷达、电子战和安全通信系统中提供改进的灵活性和性能。

06未来方向和新兴技术

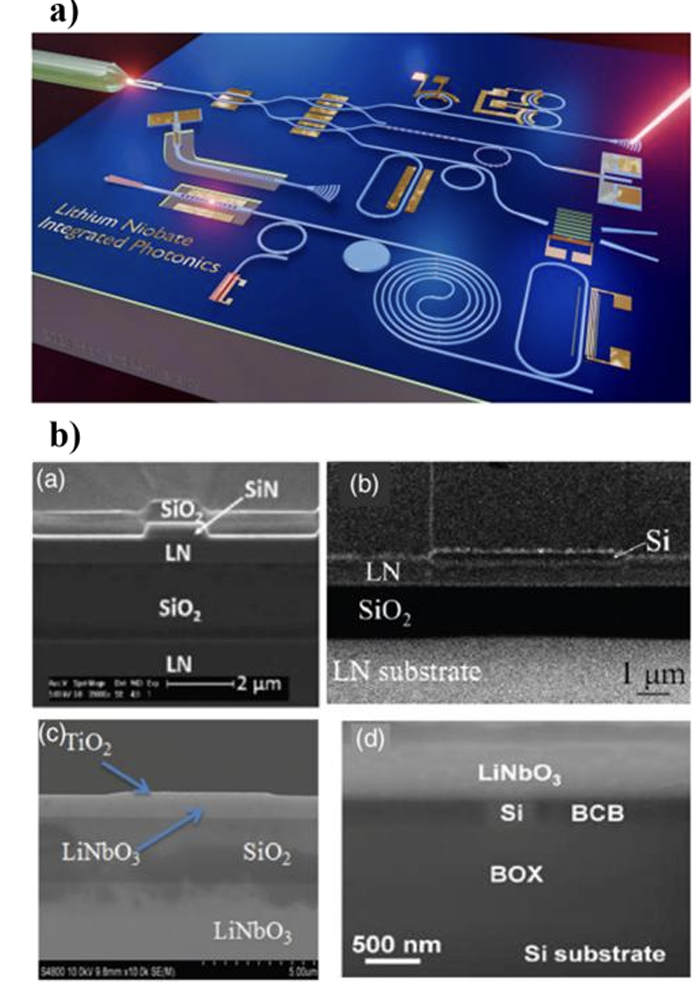

随着CPO和3D光电子技术的持续发展,几个前瞻性研究领域有望塑造集成光学技术的未来发展。下一代硅基光电子集成越来越多地探索纯硅之外的异质材料平台,特别是薄膜铌酸锂调制器,可提供超低驱动电压和高线性度,用于实现高阶调制格式。最近的工作已经证明使用基于铌酸锂的集成调制器进行320吉比特每秒相干传输,具有出色的插入损耗和带宽特性。

图8:薄膜铌酸锂上的集成光电子器件,显示了器件结构和混合波导配置,可实现高性能调制。

与此同时,III-V材料在硅上的异质集成寻求克服硅平台上的激光器集成挑战。通过将铝镓铟砷增益区域键合到硅波导上,已经演示了混合III-V-硅激光器,而在300毫米晶圆上直接外延生长量子点激光器表明了真正单片解决方案的潜力。使用晶圆键合技术将超低噪声激光器3D集成到硅基光电子上强调了先进封装如何将性能推向远超传统2D方法的水平。

人工智能工作负载的快速增长引发了对光计算和光电子加速器的强烈兴趣,这些加速器可以提供比纯电子系统更高的吞吐量和更低的延迟。用于深度学习推理的相干纳米光子线路的突破性演示说明了全光矩阵乘法的能源效率优势。最近的光电子张量核心扩展了这种方法,在集成光子线路中显示并行卷积操作。在2.5D或3D封装中与电子器件共同集成的更大规模硅光电子加速器可以实现多吉赫兹操作,延迟仅为几纳秒,为边缘和数据中心的人工智能开辟了新的可能性。

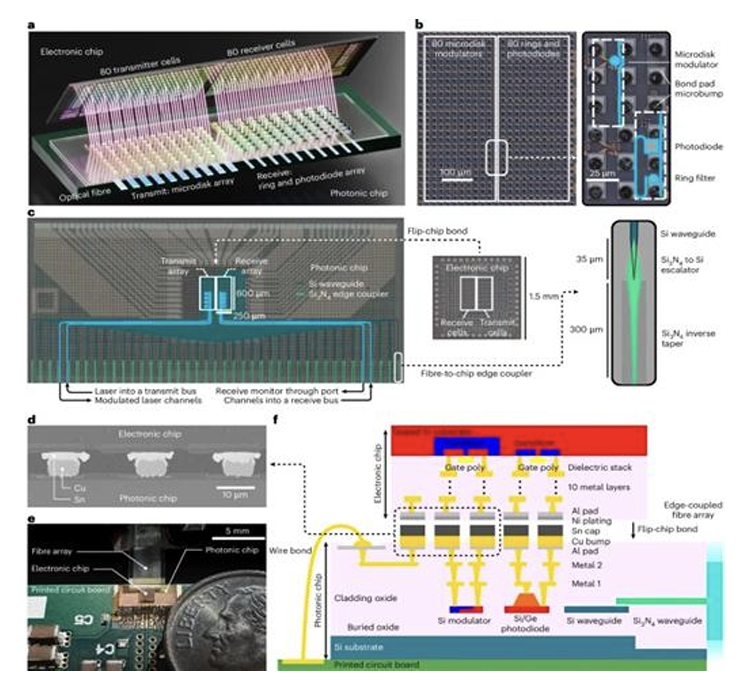

图9:3D集成光电系统,将电子单元阵列与光电子器件阵列结合用于光计算应用。

量子信息科学已经转向集成光子技术作为可扩展、稳定和高保真量子系统的关键推动者。开发量子互连以光学方式连接分布在多个节点上的量子比特已成为实现分布式量子计算和安全量子通信的核心挑战。在金刚石和III-V半导体中的固态量子比特方面已经取得了显著进展,其中片上光子线路在量子处理元件之间路由单光子或纠缠光子对。具有远程纠缠的多节点量子网络的演示强调了在集成平台上构建多用户量子通信系统的可行性。

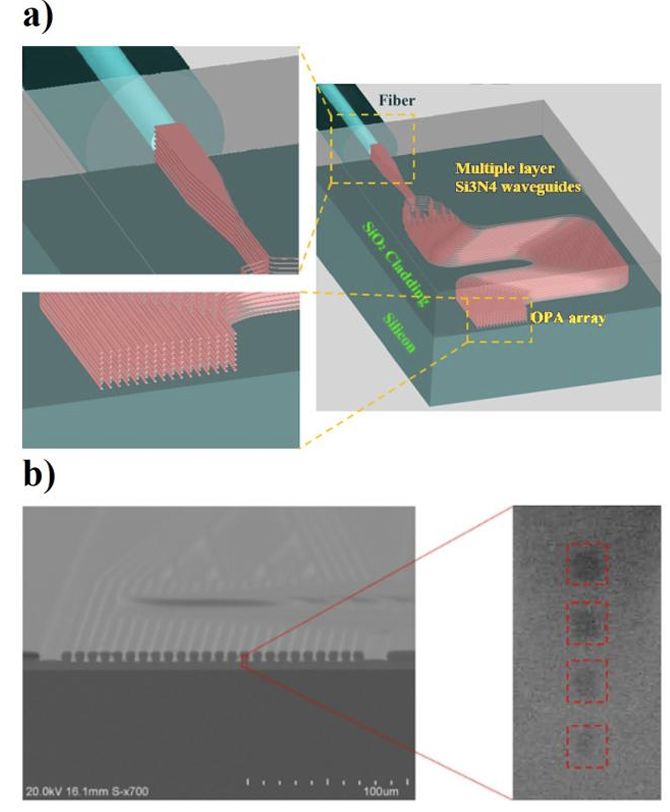

单片集成与基于chiplet方法之间的基本辩论继续塑造集成光子技术的未来轨迹。单片解决方案承诺在单一工艺流程中无缝共同制造电子和光电子器件,可能最小化寄生损耗并在规模上优化系统性能,尽管工艺复杂性和良率仍然是显著障碍。基于chiplet的封装通过允许在将光电子芯片和电子ASIC组装到interposer上之前分别优化而提供设计灵活性,这种策略已经在一些高带宽光学输入输出chiplet中商业化,可以与计算芯片共封装以实现多太比特数据速率。最优的前进路径可能最终结合两种方法的优点,单片集成选定的光电子元件,同时将专用组件(如某些激光源)卸载到可以通过晶圆键合或倒装芯片assembly无缝集成的chiplet上。

图10:为单模光纤与芯片之间的高耦合效率而设计的多层氮化硅基3D光学相控阵,包括示意图和扫描电子显微镜图像。

随着人工智能和云规模环境中的数据吞吐量继续呈指数增长,CPO将成为未来交换机和加速器设计不可或缺的部分。先进封装技术、异质集成技术和新型光电子材料的持续融合为实现长期追求的个位数甚至亚皮焦耳每比特互连目标创造了路径。通过光子技术研究人员、封装工程师、系统架构师和制造专家之间持续的多学科协作,CPO和3D光电子集成将塑造未来计算和网络系统的性能、可扩展性和能源效率。

关于我们:

天府逍遥(成都)科技有限公司(Latitude Design Automation Inc.)是一家专注于半导体芯片设计自动化(EDA)的高科技软件公司。我们自主开发特色工艺芯片设计和仿真软件,提供成熟的设计解决方案如PIC Studio、MEMS Studio和Meta Studio,分别针对光电芯片、微机电系统、超透镜的设计与仿真。我们提供特色工艺的半导体芯片集成电路版图、IP和PDK工程服务,广泛服务于光通讯、光计算、光量子通信和微纳光子器件领域的头部客户。逍遥科技与国内外晶圆代工厂及硅光/MEMS中试线合作,推动特色工艺半导体产业链发展,致力于为客户提供前沿技术与服务。

- 随机文章

- 热门文章

- 热评文章

- 泰克示波器MSO6B与上一代MSO5对比

- Modbus到ProfibusDP:无缝通讯秘籍!

- NVMe IP高速传输却不依赖XDMA设计之二:PCIe读写逻辑

- 工业通信大集结:TSN、PROFINET、EtherCAT交换机集中发布,光路科技展示核心产品

- 浪涌保护器:现代电气系统的“隐形守护者”

- 虹科免拆案例 | 2019款保时捷卡宴插电式混合动力车空调偶尔不制冷

- 磁致伸缩位移传感器在高温下的信号衰减问题解析

- 荣晟环保(603165):浙江荣晟环保纸业股份有限公司第八届监事会第十一次会议决议