以下文章来源于AdriftCoreFPGA芯研社,作者CNL中子

前言

在 SoC、FPGA IP、外设控制器等系统中,配置通路(Configuration Bus) 几乎无处不在——寄存器读写、状态回读、DMA 触发、控制接口、模块初始化这些都离不开一条稳定可靠的配置总线。

在实际设计中,工程师往往需要在 APB、AHB、AXI-Lite 之间做权衡与选择。

然而,这三种协议各有优点,也各自带着不容忽视的工程痛点。

虽然配置通路本身属于低速域,看起来不复杂,但真正落地到几十个外设、跨时钟域、压 timing、做slice、处理读写语义一致性时,往往会暴露出各种棘手问题。

本文将基于实际工程经验,讨论 APB / AHB / AXI-Lite 在真实项目中的常见痛点和使用场景。如果你有不同的观点、踩过更深刻的坑,或有更好的架构方法,欢迎在评论区一起交流。

APB

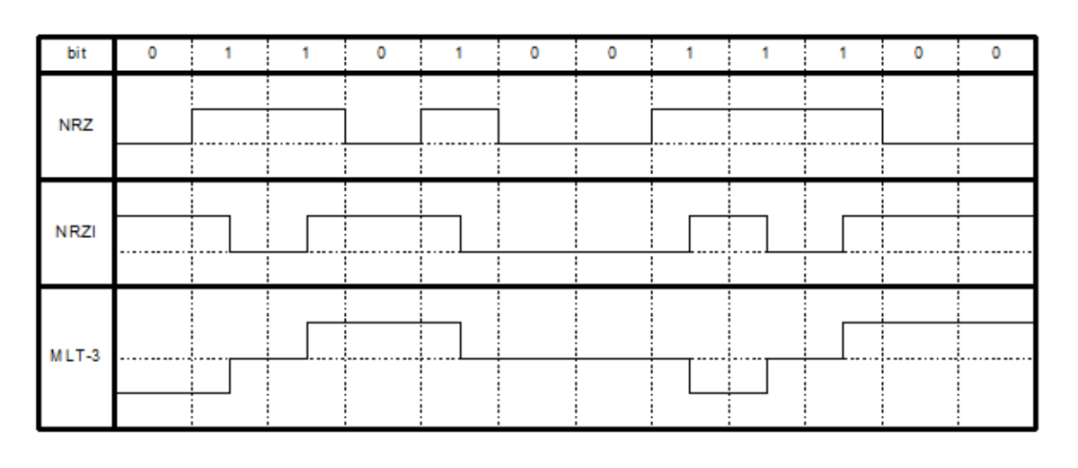

APB 可以说是最简单的一类总线协议,在众多 IC 设计和 FPGA 项目中都被大量使用。它无流水、无突发,控制信号少、时序关系简单,在所有常见总线中资源占用理论上最小。其优点是简单、稳定、易集成;缺点同样明显:带宽与性能有限。

在大多数配置场景中,只是写寄存器、回读状态,对性能需求并不高,因此 APB 能在各类 SoC 中存活超过 20 年也就不足为奇。

然而,APB 的简单只在系统规划良好的前提下成立。当初期没有做好 APB slave地址空间的规划,例如一个 master 需要连接几十路 slave 时,复杂度就会急剧上升。

时序收敛难度陡增

APB 信号数量虽然不多,但组合逻辑比例很大。当你把几十路 PSEL、读写分配、多路选择器等全部堆在一个大型crossbar中,综合之后会出现典型问题:

• 长组合路径链条过多

• 分布式逻辑跨区域布局

• 极高的 Fanout

• 全局走线拉得非常长

最终结果很容易是:时序全面崩坏。

APB 极不适合做slice/pipeline

在 SoC 中通过切关键路径插一拍,是传统且有效的时序优化手段。但 APB 具有一些独特缺陷,使得 pipeline 十分困难:

• APB 没有完整的握手机制

• 时序依赖固定的两拍协议 + 半同步行为

• 读写共享通路,不像 AXI 那样天然分离

• 写路径可能只有一条,而 pready / prdata 却可能来自几十路,从而难以统一处理

在这种情况下,随意插入一拍非常容易破坏协议timing diagram,例如:

• PSEL / PENABLE 的时序关系被打乱

• PREADY 反馈延迟不一致

• PRDATA 返回周期无法与手册周期要求匹配

即便你强行做成了slice,它也不会像 AXI-Stream 那样形成一致、标准的pipeline结构。由于读写通路不分离、通道数不对称、反馈路径复杂,实现最终往往会变成一坨难以维护的“屎山”。

更糟糕的是,当系统已经发展到几十路slave,这时候想再做分区规划、把 slave 进一步级联或分层,往往已经为时已晚。此阶段想要重构 APB 配置通路意味着:

需要重新推导、重新规划整个路径,工作量巨大。

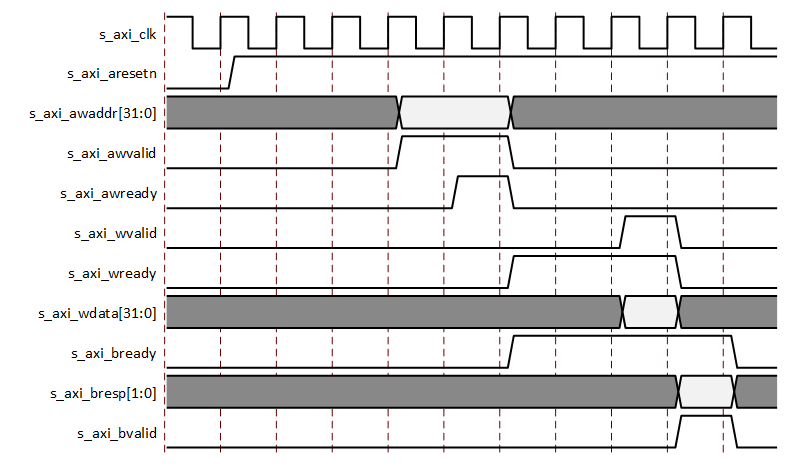

AXI-Lite

AXI-Lite 是 AXI 协议的精简版本,主要用于配置类访问。其请求、数据与响应完全分离,包含五个独立通道:AR、AW、W、R、B。

与完整 AXI 不同,AXI-Lite 不支持 burst,也没有 ID,因此仅支持单次访问。然而,它允许:

• AR 通道连续握手(连续发起读请求)

• AW/W 通道连续握手(连续发起写请求)

• 读写并行执行(读写通道完全独立)

因此在 Xilinx IP、Intel IP 等主流平台中,AXI-Lite 是默认的配置通路方案。

多子系统下的顺序不可控问题

在 多个 Slave 并存的系统中,AXI-Lite 的并行读写机制可能会让顺序处理变得异常棘手。

例如,你依次发起了两次读访问:

1. Read SLAVE_A 2. Read SLAVE_B

AXI-Lite 不保证返回顺序与发出顺序一致。

由于读通道是完全独立且可并发的,SLAVE_B 的响应可能比 SLAVE_A 更早返回。

在多 SLAVE 情况下,读写之间不存在全局顺序,你以为“先发起的 READ 会先回来”,但协议并不这么保证。

因此,如果系统逻辑需要顺序语义(例如状态机严格依赖先后顺序),就需要额外的顺序控制手段,例如:

• Ordering FIFO(请求顺序缓存)

• tag(人为添加事务 ID)

• 状态同步机制

• 或者直接给每个子系统分配独立的控制端口

这些都是额外的工程成本。

在特殊场景中,如果连续访问的是同一个 slave,内部顺序通常不会被打乱,但跨 slave 就必须显式处理。

硬件资源与结构复杂度更高

由于 AXI-Lite 的五通道是分离的,并且允许连续发起请求,因此需要一定的 outstanding 能力(哪怕只有 1 层),也导致:

• 接线较 APB 明显复杂

• 资源成本更高

• crossbar、仲裁、通道同步逻辑更重

换句话说,AXI-Lite 在灵活性和并行性上优于 APB,解决了APB难以做slice/pipeline的痛点,但其工程成本和硬件复杂度也随之提高。

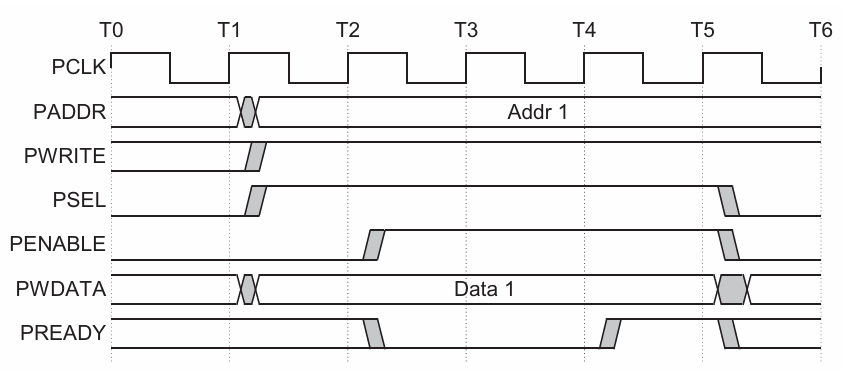

AHB-Lite

AHB-Lite 是 AMBA AHB 协议的精简版本,主要用于中等带宽的外设访问与配置类场景。

相比完整AHB,AHB-Lite 去掉了多主机仲裁(single master) ,但保留了 AHB 的关键特性:

流水化、单周期地址阶段 + 数据阶段解耦、支持 burst、支持 back-pressure。

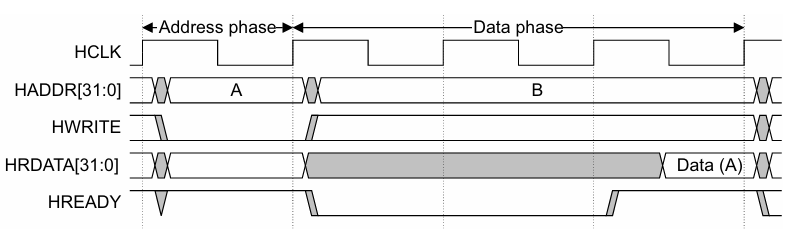

在 AHB-Lite 中,每一次访问由两部分组成:

• 地址阶段(Address Phase) :由 HADDR、HTRANS、HWRITE 等信号描述

• 数据阶段(Data Phase) :由 HRDATA、HWDATA、HREADY、HRESP 等信号描述

两个阶段是 严格对齐但可流水化 的,也就是说:

• 当前周期发送地址

• 下一个周期就可以发送下一次地址

• 数据返回与否由 slave 的 HREADY 控制

这种结构比 APB 灵活,也比 AXI 简单。

但是,AHB-Lite 也存在一些现实痛点。

HREADY 同时影响控制与数据阶段

AHB 最让工程师头疼的地方在于 HREADY 信号承担了两重语义:

• 表示“本拍的数据是否有效”

• 表示“下一拍的地址/控制阶段是否可以推进”

这会带来典型的工程不优雅行为:上一个数据阶段的 ready 会影响当前地址/控制阶段。

例如,在写 SLAVE_A 的数据的下一拍,如果要访问 SLAVE_B,HREADY 已经切换到 SLAVE_B 上,而 SLAVE_A 的数据阶段可能还未完成。

因此在设计 slave 时,通常需要处理两个 ready 信号:

• 总线侧的 HREADY(输入 ready),用于控制数据传输

• Slave 输出的 HREADY,用于表明数据已经被接收

主流 FPGA 支持不足

在 FPGA 工程中,AHB 还存在另一个痛点:生态与工具支持有限。

• 主流 FPGA 的生态几乎都是 AXI 为主

• AHB 不像 APB 那样简单,也缺少官方 interconnect IP

• Vivado/Quartus 等工具对 AHB 的参考设计和自动生成支持非常有限

• 很少有工程师愿意在 FPGA 中自己实现一套 AHB 互联

因此,尽管 AHB 有其优势,实际使用时需要付出更多工程成本。

AHB 的工程实用性

尽管存在这些痛点,但在 特定规模的配置总线场景 下,AHB-Lite 仍然非常实用:

• 它解决了 APB 难以做 pipeline 的问题

• 它避免了 AXI-Lite 需要手动管理顺序语义的麻烦

• 同时,AHB-Lite 的复杂度介于 APB 和 AXI-Lite 之间,既不太弱,也不过于臃肿

因此,对于中等规模的配置通路,AHB-Lite 往往是工程上最折中的选择。

写在最后

在实际 SoC、FPGA IP 与外设控制器设计中,配置总线的选择往往是权衡稳定性、性能与工程成本的折中。

| 总线类型 | 优点 | 缺点 | 工程适用场景 |

|---|---|---|---|

| APB | 简单、易集成、资源占用低 | 读写共享通路、不易 pipeline、时序闭合难 | 小规模配置总线、低速寄存器访问 |

| AXI-Lite | 读写通道独立、支持并行、可连续请求 | 顺序不可控、通道多、硬件成本高 | 高并发配置需求、需要多 master/多 slave 支持 |

| AHB-Lite | 地址/数据阶段解耦、可流水化、支持 back-pressure | HREADY 双重语义复杂、FPGA 工具生态弱 | 中等规模配置总线、需要 pipeline 且顺序重要 |

从工程实践来看:

APB 适合简单、低速配置场景,资源占用最小,但在系统规模扩大、跨时钟域或多 slave 情况下容易遇到时序收敛和 slice/pipeline 难题。

AXI-Lite 灵活性高,读写通道独立且可并行,但需要手动管理顺序语义,硬件复杂度和接线成本高。

AHB-Lite 在中等规模配置总线中最为折中:它既解决了 APB 难以 pipeline 的痛点,也规避了 AXI-Lite 的顺序管理麻烦,同时硬件复杂度适中,但需要处理 HREADY 双重语义,并且在 FPGA 中缺乏工具支持。

- 随机文章

- 热门文章

- 热评文章

- ModbusRTU转profibusDP网关与电动机保护器通讯案例

- ModbusRTU转profibusDP网关如何把RAC300控制器接入到西门子plc系统

- ModbusRTU转profibusDP网关与RAC400控制器06功能码的应用

- 启源芯动力罗源湾补能中心项目实证:钢-港短倒场景降碳可复制新路径

- 光纤是干嘛的

- 数据采集卡的模拟输入信号到底应该怎么接线?

- 可编程低抖动VCXO:支持±150ppm拉力范围与1~3天快速交付

- 多功能+高扩展能力加持,Air8000开发板最新资料